Home page

Dec 19, 2011 Note there is a new page now: www.theover.org/Fpgasynth , this is the old one.

This page is about my use of the materials from www.fpga.synth.net which is a very interesting set of working sound synthesizer designs with Open Source verilog and assembly files, which I´m in the process of trying or adding to.

I of course have done work in synthesis myself (Open Source DSP analog simulation with programmable logic, and a complicated string simulator), and also with FPGA´s (like here, but that isn´t sound synthesis).

In fact I´ve recently added a wiki to the server, see this page about the same subject.

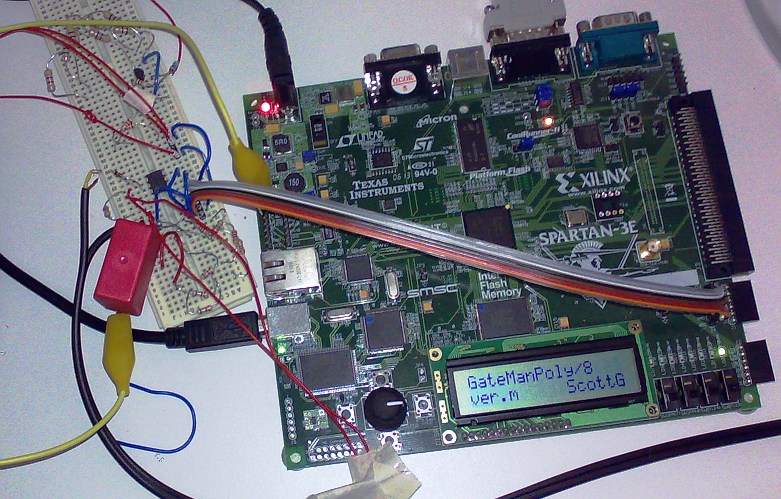

My Xilinx Spartan 3E(500) Startkit connections

Yesterday evening I made these connectionsOpto coupler: MCT2 (240 ohms collector resistor)

My test setup of the night (literally)

Audio: output A coupled via 33 micro Farad (non-electrolytic)

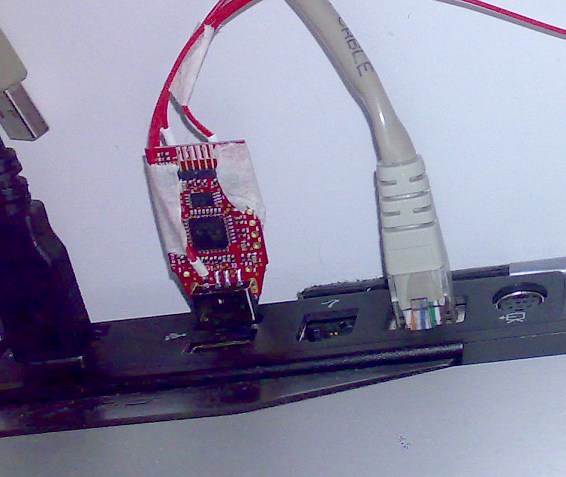

Programmer link: using serial port and a windows machine with serial connection, but currently from the same machine as the programmer usb link, using a modified Texas Instruments eZ430-RF2500 usb programmer/serial converter board:

which uses 9600 baud, which required me to change TTYuartrx.v here:

// SRG added this baud rate clock:and I made a connector for pin D7, near the midi connector, which is connected to the TI serial link output, so the UCF connection file GateManPoly.ucf changed here:

//-----------------------------------------------------------

// 16x baud clock fixed at MIDI rate 115.2 or 19.2 Kbaud (clk = 50MHz)

//-----------------------------------------------------------

always @ ( posedge clk )

begin

// 27 states for 115200 baud (27.126736111...)

// if ( baudcounter == 8'd26 )

// 163 states for 19200 baud (162.7604167)

// if ( baudcounter == 8'd162 )

// 326 states for 9600 baud (2x163)

if ( baudcounter == 9'd325 )

begin bclk <= 1'b1; baudcounter <= 0; end // one less because we stat at 0

else

begin bclk <= 1'b0; baudcounter <= baudcounter + 8'b1; end

end

# DCE serial connectionsThe midi signal comes from a years old but great Yamaha S90 synthesizer, set to analog midi output, with a 4 meter cable.

##NET "TTY_In" LOC = "R7" | IOSTANDARD = LVTTL ;

NET "TTY_In" LOC = "D7" | IOSTANDARD = LVTTL ;

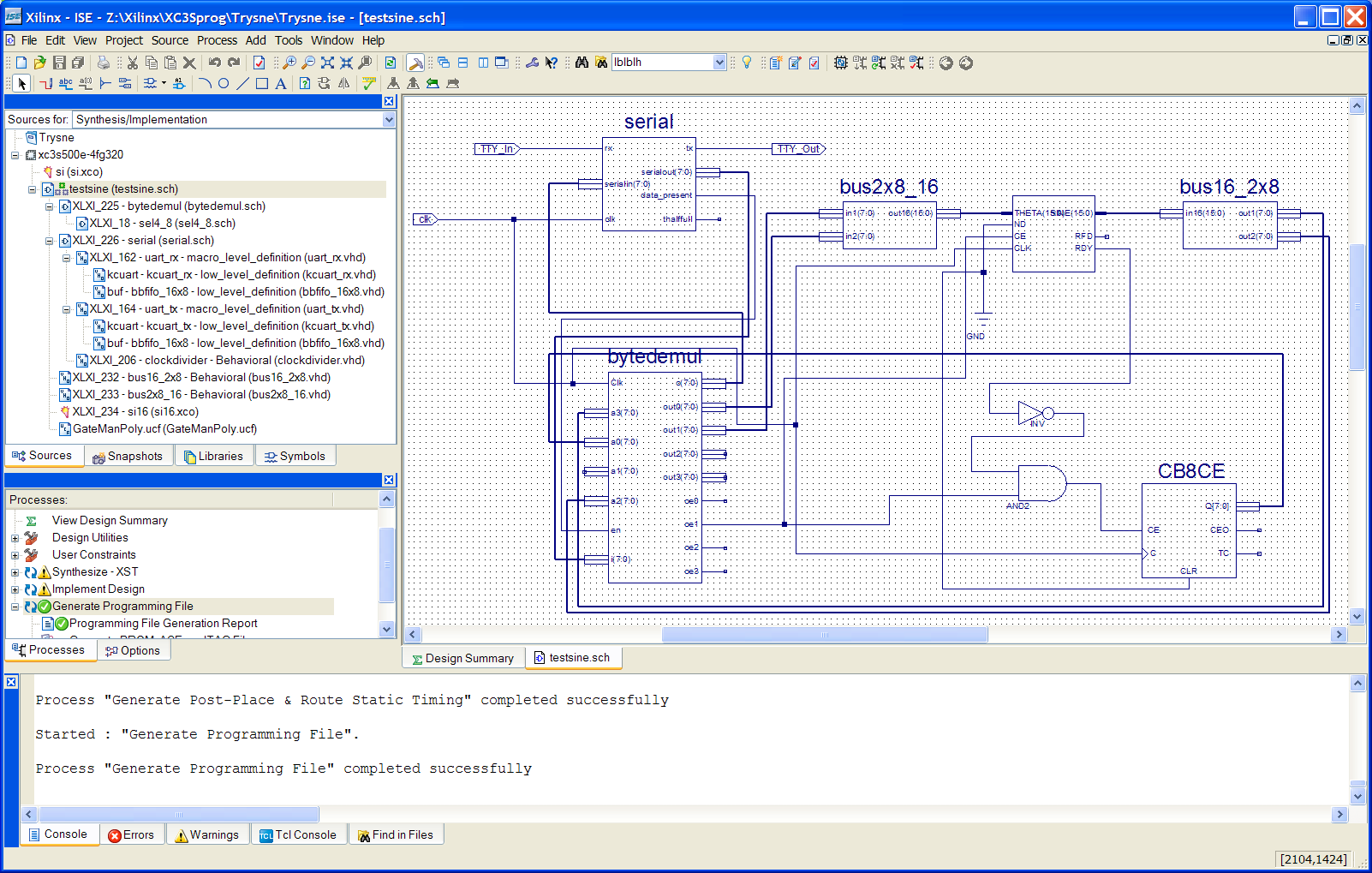

I succesfully synthsized using the ISE 8.2.03i Webpack environment on XP pro these projects:

analog

BassDaWG

Midimon which I used to test and modify the midi interface

pub (polysynth)

I had great fun trying these designs out, the high sampling rate and power of the FPGA have been used good. Of course I think about using some great DA chips I got from TI (on for instance a 6 channel superaudio or 192/24 high quality converter, and I got an AD for that, too), or maybe a TOS output, I´ve started that but didn´t finish it.

I´ve made a prom programmer file (.mcs) for the modified polysynth design, which is here. It doesn´t make sound until you program a sound patch in the board via the 9600 kbs (3.3 Volts max) D7 pin!

Some patches for the Gate Man Poly

The Gate

Man

Poly is a very interesting design for the Spartan 3E starter

kit from Xilinx, which has a size 500 FPGA on it, along with

connections and quite a few peripherials, made by Scott

Gravenhorst (I presume he is from PAiA and the fatman synth (note

from later: he's made additions to their designs, but is not from that

company)). So I didn´t make

this design,

I tried it and want to add to it!These patches I made with the Programmed board, with midi interface with a Conrad opto coupler chip, and a link with a Lexicon Omega AD/DA converter from one DA converter output (A), and a programmer link with a notebook, just like the silicon compilation of the design was done on a Dell M90 precision notebook, and the programming too (I used IMPACT 7.2 which works fast if I don´t switch of the xilinx board). The sound programmer link is driven by the supplied visual basic program: